Power Management Solutions

The TPS65217C power management device is used along with a separate LDO to provide power to the system. The TPS65217C version provides for the proper voltages required for the DDR3L. This is the same device as used on the original BeagleBone with the exception of the power rail configuration settings which will be changed in the internal EEPROM to the TPS65217C to support the new voltages.

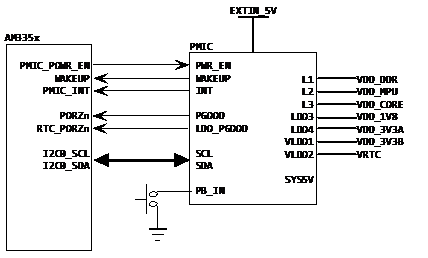

Figure 4-4

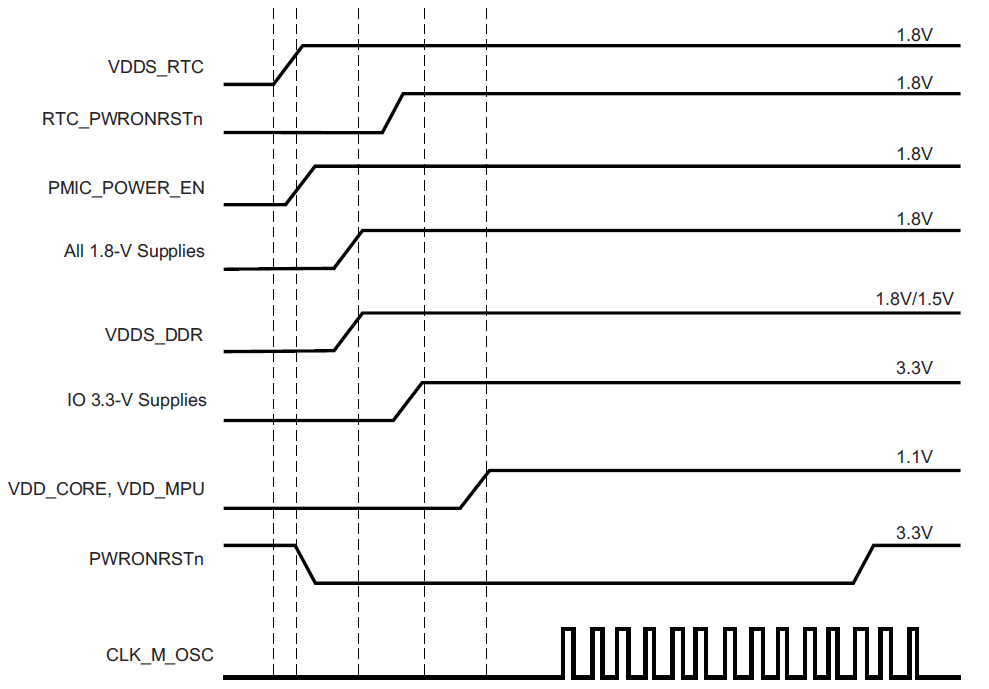

Power Timing

Processors power up follow the timing requirements as Figure 4-5. First is VDD_RTC, after PMIC_POWER_EN, then is VDD_1V8, core, MPU, peripherals and so on.

Figure 4-5

Signal

- PMIC_POWR_EN: On power up the VDD_RTC rail activates first. After the RTC circuitry in the processor has activated it instructs the TPS65217C to initiate a full power up cycle by activating the PMIC_POWR_EN signal by taking it HI. When powering down, the processor can take this pin low to start the power down process.

- WAKUP: The WAKEUP signal from the TPS65217C is connected to the EXT_WAKEUP signal on the processor. This is used to wake up the processor when it is in a sleep mode. When an event is detected by the TPS65217C, such as the power button being pressed, it generates this signal.

- PMIC_INT: The PMIC_INT signal is an interrupt signal to the processor. Pressing the power button will send an interrupt to the processor allowing it to implement a power down mode in an orderly fashion, go into sleep mode, or cause it to wake up from a sleep mode. All of these require SW support.

- PMIC_PGOOD: Once all the rails are up, the PMIC_PGOOD signal goes high. This releases the PORZn signal on the processor which was holding the processor reset.

- LDO_GOOD: As the RTC circuitry comes up first, this signal indicates that the LDOs, the 1.8V VRTC rail, is up and stable. This starts the power up process.

- I2C: Is the control interface between the processor and the TPS65217C. It allows the processor to control the registers inside the TPS65217C for such things as voltage scaling and switching of the input rails.

- PB_IN: The PMIC_INT signal is an interrupt signal to the processor. Pressing the power button will send an interrupt to the processor allowing it to implement a power down mode in an orderly fashion, go into sleep mode, or cause it to wake up from a sleep mode. All of these require SW support.

Power source

- VDDS_DDR: Use for DDR, usually 1.5v, adjust the voltage to reduce power consumption

- VDD_MPU: Use for MPU Up to 1.2A, this voltage can change by I2C, thus changing the MPU clock speed.

| OPP | VDD_MPU | Frq |

|---|---|---|

| OPP50 | 0.95V | 300MHz |

| OPP100 | 1.1V | 600MHz |

| OPP120 | 1.2V | 720MHz |

| Turbo | 1.26V | 800MHz |

| Nitro | 1.325V | 1GHz |

Table 4-1

- VDD_CORE: Use for core of AM335x, Because MCC-AM335X-Y use the DDR3,so this voltage must be 1.1V.

- VDD_3V3A: Use for IO of AM335x, which is 3.3V on the CPU Module.

- VDD_3V3B: Another 3.3V voltage. It will output of CPU Module. Supply the base board which using the 3.3V IO.

- VDD_1V8: Use for the 1.8V of AM335x.